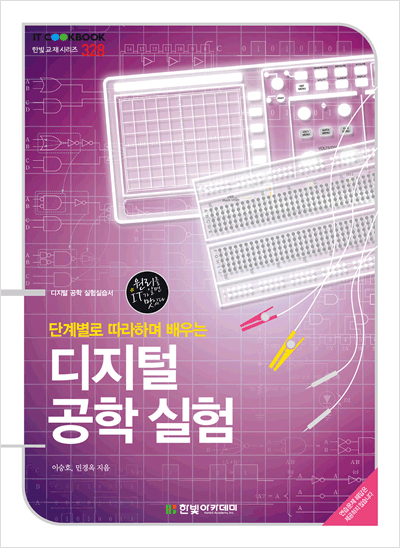

지은이 소개 • 02

지은이 머리말 • 04

강의 계획 • 06

강의 보조 자료 및 참고 자료 • 07

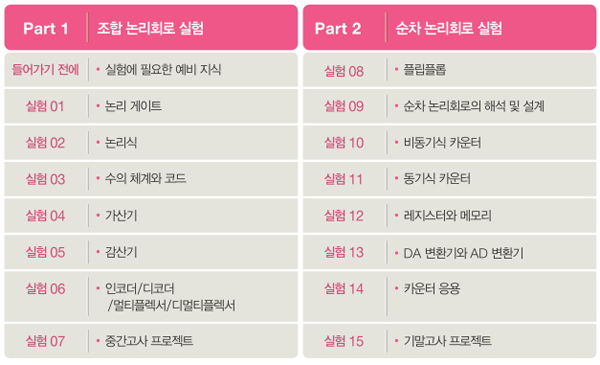

1부. 조합 논리회로 실험

들어가기 전에|실험에 필요한 예비 지식 ∙ 13

1 아날로그와 디지털 · 13

2 디지털 집적회로 · 15

3 저항 및 콘덴서 읽는 법 · 25

4 스위치의 조합 및 접점 · 29

5 다이오드와 트랜지스터 · 33

6 실험 장비 사용법 · 37

실험 01|논리 게이트 ∙ 51

1.1 BUFFER 게이트, NOT 게이트 · 51

1.2 AND 게이트, NAND 게이트 · 59

1.3 OR 게이트, NOR 게이트 · 66

1.4 XOR 게이트, XNOR 게이트 · 73

실험 02|논리식의 간소화 ∙ 81

2.1 논리식의 표현 및 간소화 · 81

2.2 NAND와 NOR 게이트만을 사용한 논리회로 · 96

실험 03|수의 체계와 코드 ∙ 103

3.1 진법과 진법 변환 · 103

3.2 8421 코드와 BCD 코드 · 109

3.3 3초과 코드 · 114

3.4 그레이 코드 · 119

실험 04|가산기 ∙ 124

4.1 가산기 · 124

4.2 반가산기 · 126

4.3 전가산기 · 130

실험 05|감산기 ∙ 137

5.1 감산기 · 137

5.2 반감산기 · 139

5.3 전감산기 · 143

실험 06|인코더/디코더/멀티플렉서/디멀티플렉서 ∙ 150

6.1 인코더 · 150

6.2 디코더 · 155

6.3 멀티플렉서 · 166

6.4 디멀티플렉서 · 171

실험 07|중간고사 프로젝트 ∙ 174

7.1 진법 변환 · 174

7.2 불 대수 법칙 · 175

7.3 4변수 카르노 맵 · 176

7.4 5변수 카르노 맵 · 177

7.5 BCD의 9의 보수 발생기 · 178

7.6 2진 4비트 가산기/감산기 · 181

7.7 3비트 패리티 생성기/검사기 · 184

7.8 3비트 크기 비교기 · 189

7.9 4×2 우선순위 인코더 · 192

7.10 7세그먼트 디코더 · 195

7.11 BCD 가산기 · 199

2부. 순차 논리회로 실험

실험 08|플립플롭 ∙ 205

8.1 래치 회로 · 205

8.2 플립플롭의 개요 · 211

8.3 RS 플립플롭 · 219

8.4 D 플립플롭 · 222

8.5 JK 플립플롭 · 224

8.6 T 플립플롭 · 227

실험 09|순차 논리회로의 해석 및 설계 ∙ 229

9.1 순차 논리회로의 해석 · 229

9.2 순차 논리회로의 설계 · 239

실험 10|비동기식 카운터 ∙ 248

10.1 2진 비동기식 카운터 · 248

10.2 10진 비동기식 카운터 · 254

10.3 리셋과 프리셋을 이용한 6진 비동기식 카운터 · 260

10.4 결합형 비동기식 카운터 · 264

실험 11|동기식 카운터 ∙ 268

11.1 D 플립플롭을 이용한 6진 동기식 카운터 · 268

11.2 JK 플립플롭을 이용한 7진 동기식 카운터 · 274

11.3 링 카운터와 존슨 카운터 · 279

실험 12|레지스터와 메모리 ∙ 288

12.1 레지스터 · 288

12.2 시프트 레지스터 · 296

12.3 메모리 · 299

실험 13|DA 변환기와 AD 변환기 ∙ 308

13.1 DA 변환기 · 308

13.2 AD 변환기 · 316

실험 14|카운터 응용 ∙ 326

14.1 타이머 캡처 · 326

14.2 ON 타이머 · 331

14.3 OFF 타이머 · 334

실험 15|기말고사 프로젝트 ∙ 338

15.1 멀티플렉서를 이용한 플립플롭 설계 · 338

15.2 새로운 플립플롭 설계 · 341

15.3 순차 논리회로의 해석 · 343

15.4 순차 논리회로의 설계 · 345

15.5 리셋이 없는 비동기식 T 플립플롭 6진 카운터 설계 · 349

15.6 동기식 JK 플립플롭 12진 카운터 설계 · 350

15.7 동기식 JK 플립플롭 3비트 홀수 카운터 설계 · 354

15.8 병렬 로드 기능이 있는 동기식 4진 카운터 설계 · 357

15.9 주소 영역 디코더 설계 · 361

15.10 적산 타이머 설계 · 365

15.11 리트리거블 타이머 설계 · 366

찾아보기 ∙ 368